《數(shù)字邏輯設(shè)計(jì)及應(yīng)用 本科1 答案Word版》由會(huì)員分享����,可在線閱讀,更多相關(guān)《數(shù)字邏輯設(shè)計(jì)及應(yīng)用 本科1 答案Word版(3頁(yè)珍藏版)》請(qǐng)?jiān)谘b配圖網(wǎng)上搜索�。

1、姓名_ 專業(yè)名稱_班號(hào)_學(xué)號(hào)_教學(xué)中心_ 密 封 線 電子科技大學(xué)網(wǎng)絡(luò)教育考卷(A卷)(20 年至20 學(xué)年度第 學(xué)期)考試時(shí)間 年 月 日(120分鐘) 課程 數(shù)字邏輯設(shè)計(jì)及應(yīng)用(本科) 教師簽名_ 大題號(hào)一二三四五六七八九十合 計(jì)得 分一�����、填空題(每空1分�����,共20分)1���、請(qǐng)完成如下的進(jìn)制轉(zhuǎn)換:22.7510= 10110.11 2= 26.6 8= 16.C 16�����;2、F6.A16= 246.625 10= 0010 0100 0110.0110 0010 0101 8421BCD= 0101 0111 1001.1001 0101 1000 余3碼3�����、-9910的8位(包括符號(hào)位)二進(jìn)制

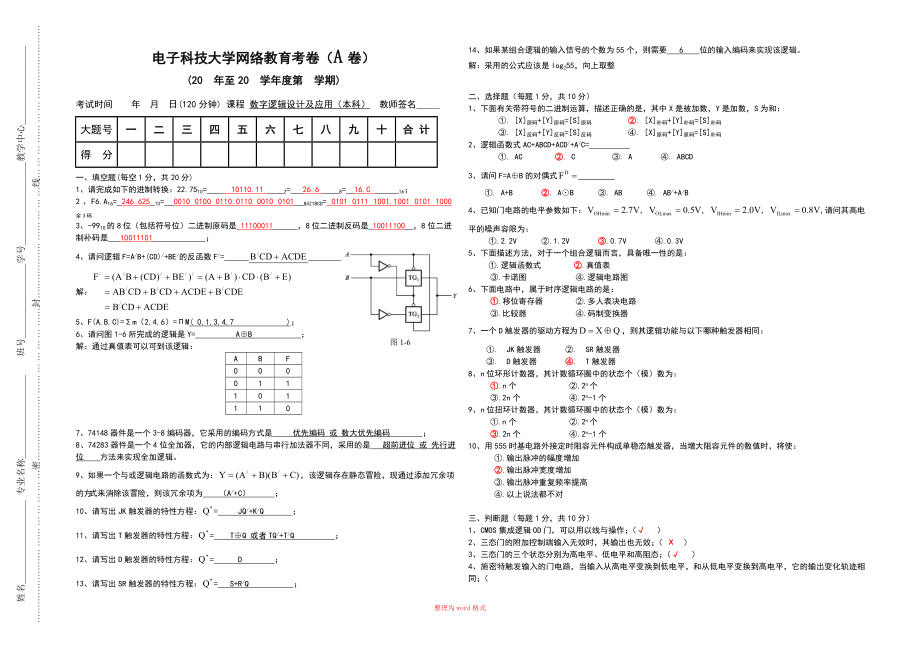

2��、原碼是 11100011 ��,8位二進(jìn)制反碼是 10011100 �����,8位二進(jìn)制補(bǔ)碼是 10011101 �;圖1-64����、請(qǐng)問(wèn)邏輯F=A/B+(CD)/+BE/的反函數(shù)F/= ;解:5��、F(A,B,C)=m(2,4,6)=M( 0,1,3,4,7 )�����;6、請(qǐng)問(wèn)圖1-6所完成的邏輯是Y= AB ��;解:通過(guò)真值表可以可到該邏輯:ABF0000111011107、74148器件是一個(gè)3-8編碼器����,它采用的編碼方式是 優(yōu)先編碼 或 數(shù)大優(yōu)先編碼 �;8����、74283器件是一個(gè)4位全加器���,它的內(nèi)部邏輯電路與串行加法器不同���,采用的是 超前進(jìn)位 或 先行進(jìn)位 方法來(lái)實(shí)現(xiàn)全加邏輯��。9����、如果一個(gè)與或邏輯電路的函數(shù)式為:�,

3、該邏輯存在靜態(tài)冒險(xiǎn)����,現(xiàn)通過(guò)添加冗余項(xiàng)的方式來(lái)消除該冒險(xiǎn),則該冗余項(xiàng)為 (A/+C) ����;10、請(qǐng)寫出JK觸發(fā)器的特性方程:= JQ/+K/Q �����;11�、請(qǐng)寫出T觸發(fā)器的特性方程:= TQ 或者TQ/+T/Q ;12����、請(qǐng)寫出D觸發(fā)器的特性方程:= D �����;13、請(qǐng)寫出SR觸發(fā)器的特性方程:= S+R/Q ����;14、如果某組合邏輯的輸入信號(hào)的個(gè)數(shù)為55個(gè)�����,則需要 6 位的輸入編碼來(lái)實(shí)現(xiàn)該邏輯�����。解:采用的公式應(yīng)該是log255���,向上取整二�����、選擇題(每題1分����,共10分)1、下面有關(guān)帶符號(hào)的二進(jìn)制運(yùn)算��,描述正確的是���,其中X是被加數(shù)�����,Y是加數(shù)����,S為和:. X原碼+Y原碼=S原碼 . X補(bǔ)碼+Y補(bǔ)碼=S補(bǔ)碼 . X

4��、反碼+Y反碼=S反碼 . X原碼+Y原碼=S補(bǔ)碼 2����、邏輯函數(shù)式AC+ABCD+ACD/+A/C= . AC . C . A . ABCD3、請(qǐng)問(wèn)F=AB的對(duì)偶式 . A+B . AB . AB . AB/+A/B4�、已知門電路的電平參數(shù)如下:請(qǐng)問(wèn)其高電平的噪聲容限為:.2.2V .1.2V .0.7V .0.3V5、下面描述方法�,對(duì)于一個(gè)組合邏輯而言,具備唯一性的是:.邏輯函數(shù)式 .真值表.卡諾圖 .邏輯電路圖6����、下面電路中���,屬于時(shí)序邏輯電路的是: .移位寄存器 .多人表決電路.比較器 .碼制變換器7、一個(gè)D觸發(fā)器的驅(qū)動(dòng)方程為�����,則其邏輯功能與以下哪種觸發(fā)器相同:. JK觸發(fā)器 . SR觸發(fā)器

5�����、. D觸發(fā)器 . T觸發(fā)器8�、n位環(huán)形計(jì)數(shù)器���,其計(jì)數(shù)循環(huán)圈中的狀態(tài)個(gè)(模)數(shù)為:.n個(gè) .2n個(gè).2n個(gè) .2n-1個(gè)9����、n位扭環(huán)計(jì)數(shù)器�����,其計(jì)數(shù)循環(huán)圈中的狀態(tài)個(gè)(模)數(shù)為:.n個(gè) .2n個(gè).2n個(gè) .2n-1個(gè)10�����、用555時(shí)基電路外接定時(shí)阻容元件構(gòu)成單穩(wěn)態(tài)觸發(fā)器,當(dāng)增大阻容元件的數(shù)值時(shí)����,將使:.輸出脈沖的幅度增加 .輸出脈沖寬度增加.輸出脈沖重復(fù)頻率提高 .以上說(shuō)法都不對(duì)三、判斷題(每題1分�����,共10分)1��、CMOS集成邏輯OD門�,可以用以線與操作;( )2�、三態(tài)門的附加控制端輸入無(wú)效時(shí),其輸出也無(wú)效���;( )3�����、三態(tài)門的三個(gè)狀態(tài)分別為高電平����、低電平和高阻態(tài);( )4����、施密特觸發(fā)輸入的門電路,當(dāng)

6����、輸入從高電平變換到低電平,和從低電平變換到高電平��,它的輸出變化軌跡相同�����;( 整理為word格式 )5��、組合邏輯和時(shí)序邏輯的區(qū)別主要在于前者與時(shí)間無(wú)關(guān)�����,而后者時(shí)間的因素必須考慮進(jìn)去�;( )6��、一個(gè)邏輯的函數(shù)式并不唯一�,但是最簡(jiǎn)的與或表達(dá)式是唯一的�����;( )7���、模擬信號(hào)是連續(xù)的,而數(shù)字信號(hào)是離散的��;( )8���、當(dāng)兩個(gè)組合邏輯的真值表相同是����,則表明這兩個(gè)邏輯是相等的�;( )9、對(duì)于一個(gè)優(yōu)先編碼器而言����,當(dāng)輸入多個(gè)有效時(shí),其輸出很難討論��;( )10���、串行加法器比超前進(jìn)位加法器速度更快�,且電路更為簡(jiǎn)單;( )四�、卡諾圖化簡(jiǎn)(8分) 請(qǐng)將邏輯F(A,B,C,D) = Sm( 0, 2, 3, 5, 7, 8,

7、10, 11, 13)化成最簡(jiǎn)與或式����; 或者五、組合邏輯分析�����,要求如下:(8分)該邏輯電路圖如圖5所示����,具體要求如下:圖51、 寫出邏輯S和CO的邏輯函數(shù)式2�����、 畫出將該邏輯的真值表3��、真值表ABCISCO00000001100101001101100101 01011100111111圖6六�����、時(shí)序邏輯分析���,要求如下:(14分)邏輯電路圖如圖6所示�,請(qǐng)完成:1����、 寫出驅(qū)動(dòng)方程、狀態(tài)方程��;2�、 畫出狀態(tài)轉(zhuǎn)換圖或者狀態(tài)轉(zhuǎn)換表。解答:3.狀態(tài)表或者狀態(tài)圖:以上圖表任畫一個(gè)即得分�����。七�、組合邏輯設(shè)計(jì),要求如下:(8分)利用一塊74138芯片和一定的門電路實(shí)現(xiàn)如下邏輯:整理為word格式其中74138為3-8二進(jìn)制譯碼器解題步驟:八��、時(shí)序邏輯設(shè)計(jì)�,要求如下:(10分) 利用74163和一定的門電路實(shí)現(xiàn)如下的七進(jìn)制計(jì)數(shù)器。74163為4位的同步二進(jìn)制加計(jì)數(shù)器���。圖8第一種方法:在狀態(tài)0111時(shí)���,重置狀態(tài)到0001或�����;電路圖如下:第二種方法:在狀態(tài)1111����,通過(guò)行波輸出重置狀態(tài)到����;電路圖如下:兩種方法皆可九、時(shí)序邏輯設(shè)計(jì)�,要求如下:(10分)用mealy型時(shí)序邏輯電路設(shè)計(jì)一個(gè)101串行數(shù)據(jù)檢測(cè)的時(shí)序狀態(tài)機(jī)。要求畫出化簡(jiǎn)后的狀態(tài)轉(zhuǎn)換圖��。 友情提示:本資料代表個(gè)人觀點(diǎn)��,如有幫助請(qǐng)下載�����,謝謝您的瀏覽�! 整理為word格式

數(shù)字邏輯設(shè)計(jì)及應(yīng)用 本科1 答案Word版

數(shù)字邏輯設(shè)計(jì)及應(yīng)用 本科1 答案Word版